|

KX-CPD10

收藏

现代计算机组成与SOC创新设计开发系统 型号:KX-CPD10 然而我国高校计算机专业对等课程的教学情况总体而言不容乐观。尽管也通常包含了《计算机组成原理》的课程,但调研表明,多数学校仅将此课程定位在计算机模型认知的层面上;而在实验与实践方面,此课程的实验则主要是完成由分离元件构成的简单模型CPU的验证性实验,根本谈不上与实际工程相联系的设计,更没有国外高校类同的自主创新型CPU设计任务,以及与现代随着电子技术的发展,核心技术已经愈来愈集中在集成电路芯片和软件之中,其中CPU和OS设计技术是最为核心的技术。特别是高性能计算机技术一直是衡量国家实力的一个重要标志。美国的高校本科计算机专业中都无一不是安排了CPU硬件设计方面的课程和实验内容。例如麻省理工学院的一门相关课程就是《计算机系统设计》。学生在实验课中,须自主完成ALU、单指令周期CPU(single cycle CPU)、多指令周期CPU,乃至实现流水线32位MIPS CPU和Cache的设计;Stanford大学计算机系的本科生也有相似的课程和实验,即《计算机组成与设计》课。实验要求学生以各自独立的形式,用硬件描述语言自主实现CPU、VGA显示控制模块等接口,最后实现于FPGA中,并完成软硬件调试。此外,如University of California和Berkeley和Brigham Young University等学校在基于FPGA的超级计算机研制方面也有大量成果。计算机系统硬件设计工程相吻合的教学与实践内容。这导致了国内大多数计算机专业人才知识结构一直存在的“偏软怕硬”的缺陷。 针对这一情况, 科学出版社就于2007年就推出了《现代计算机组成原理》一书,潘松等教授编著。该教材后被评为国家级精品教材(上图。在当年国内高校所有专业教材中,评选出的218种教材中,该书是唯一涉及计算机组成原理的教材)。《现代计算机组成原理》第二版(上图。2013年)提供了基于现代计算机设计技术的关于CPU和计算机系统硬件设计理论和设计技术方面较完整和丰富的内容。其中有基于单片FPGA硬件平台的微程序控制模式的8位CISC模型计算机原理和设计技术;16位实用CISC CPU的基本原理、设计技术和创新实践指导;基于流水线技术的RISC CPU设计技术;基于32位OpenRISC1200处理器系统的SOC构建和应用设计以及基于经典处理器的8051CPU核与8088/8086 CPU核构建SOC(System Of a Chip)系统的基本理论和设计技术。对应每一章,还提供了有针对性的实验与实践项目,甚至包括激发学习者创新意识和培养创新能力的CPU创新设计竞赛项目。 近些年中,认可并实践此教材基本教学理念和教学实验内容的高校不断增加,其中许多高校的计算机专业选择此书作为教材或选择教材中提到的FPGA实验系统来完成对应的硬件实验;这些学校有西安交大、西北大学、中国人民大学、吉首大学、哈工大、北航、中国民航大学和南邮、大连理工等三十余所高校。最难得的是,最早加入这一教改行列的学校竟然是一所外语学校,即广州外语学院。该校有关老师对于外语专业学生兼修计算机软件技术和基于FPGA的计算机硬件设计技术在拓宽就业口径,提高就业率方面所表现出的优势有很高的评价。 一、模块化计算机原理与设计综合实验系统

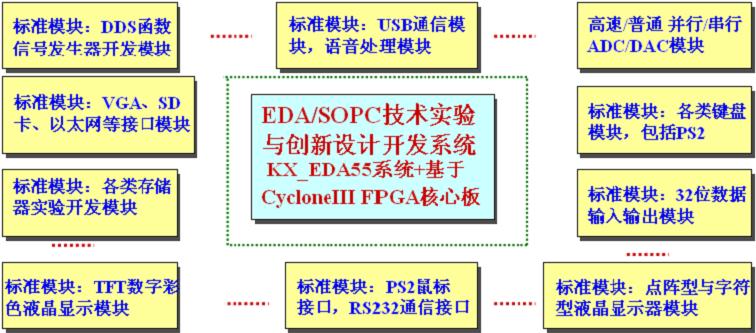

KX_CPD结构示意图。由于以上介绍的4教材中大量的实验和设计项目涉及许多不同类型的,可自由增减的扩展模块,主系统平台上有许多标准接口。以其为核心,对于不同的实验设计项目,可接插上对应的接口模块。如VGA/PS2模块、TFT数字彩色液晶模块、USB模块、宽位数据输入输出模块、SD卡模块、点阵液晶模块、各类存储器模块、各类A/D与D/A模块及各类键盘模块等;这些模块可以是现成的,也可以根据主系统平台的标准接口和创新要求由教师或学生自行开发。 通常,诸如EDA技术、计算机组成与设计、微机原理与接口技术、单片机技术等传统实验平台多数是整体结构型的,虽也可完成多种类型实验,但由于整体结构不可变动,实验项目和类型是预先设定和固定的,很难有自主发挥的余地,对于学生的创新思想与创新设计如果与实验系统的结构不吻合,便无法在此平台上获得验证;同样,教师若有新的创新型实验项目,也无法及时融入实验系统供学生发挥。因此此类平台不具备可持续拓展的潜力,也没有随需要更新和升级的能力。特别是针对EDA/SOPC的创新实验,涉及的自主设计项目更多,结构变化更大,系统更复杂,完全不可能预知最后设计出的创新项目应该包含哪些功能结构和接口模块。显然,多模块自由组合结构给出了最好的解决方案。 模块化结构给出了最好的解决方案: ○ 在创新实践中,能提供构建计算机内部结构的逻辑资源和存储器资源,丰富到足以涵盖学生的创造力所及的任何形式和规模设计项目。 ○ 在外围接口方面,除大量丰富的接口模块,如VGA、PS2、USB、SD卡、RS232串口、语音处理、AD/DA等等现成的模块外,还提供能适应实验者随时根据自己的创新实验需要,自主安排和设计新功能模块的标准接口。 ○ 从该教材多数章节也能看出,特别是对于CPU设计,将实验硬件平台定位于大规模逻辑容量的FPGA,在硬件测试,软件调试,软硬件联合开发与测试方面,以及微指令系统的实时编辑调试是十分必须的,特别是基于Quartus II平台的强大的测试工具,如Signal Tap II、In-System Sources and Probes 和In-System Memory Content Editor等具有不可替代的功能。因此,类似模块自由组合型创新设计综合实验系统,已成为高校目前十分流行的实践平台。特别指出:KX_CPD系统在除了适用于此教材中涉及的所有实验和创新实践外,还能很专业地包涵诸如数字电路与数字系统设计实验、EDA技术实验、VHDL/Verilog硬件描述语言应用实验、SOPC开发、微机原理与接口技术实验及8088/8086/8051 IP核的SOC片上系统设计等。 围绕《现代计算机组成原理》第2版教材的实验和创新实践项目,基于单片大规模FPGA所能实现的实验和SOC设计类型包括: 型号:KX-CPD10完成以下实验:

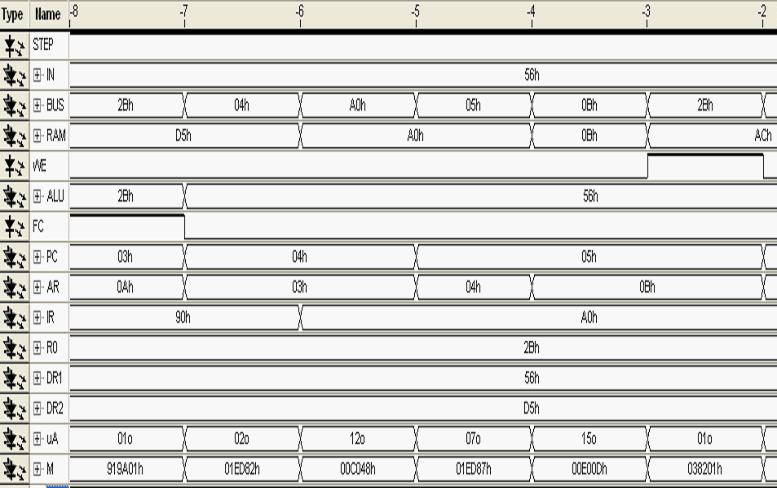

利用QuartusII的In-System Sources and Probes实时测试载入FPGA中的8位模型机执行指令的波形其中的M、uA、RAM、BUS、WE分别是微指令、微地址、存储器、总线数据、RAM写允许等信号

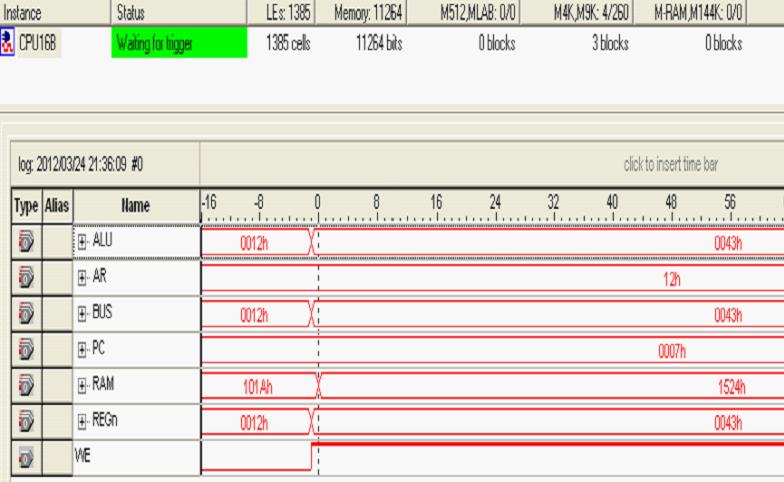

利用嵌入式逻辑分析仪对载入FPGA中的16位CPU的运行情况进行实时测试的波形和数据

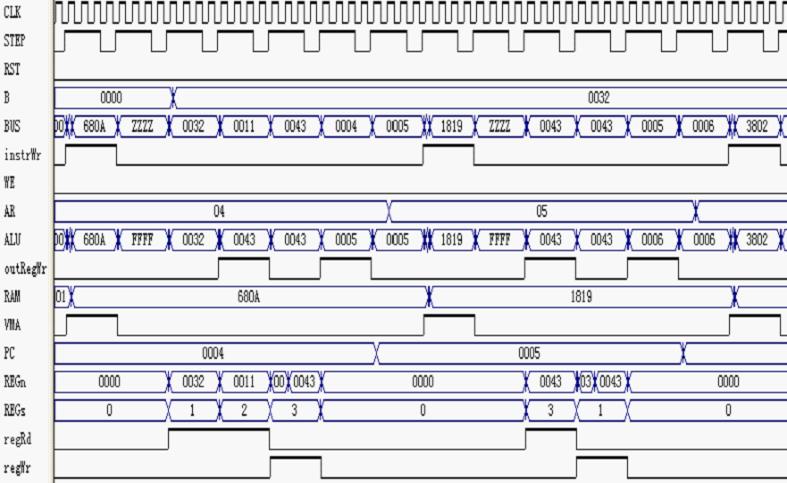

对于加法指令和存数指令在16位CPU中的执行情况的仿真波形片段

KX-CPD10配置如下:

一、基本平台 编号:A 主系统 ☆此平台最多可同时插12 块模块板。 ☆ KX_USB-Blaster2型双功能编程器:(1)USB-Blaster编程下载功能(支持AS、PS、JTAG模式):1、对FPGA/CPLD进行配置或编程;2、对配置器件EPCSx编程;3、访问和编辑FPGA内部RAM;4、调试Nios2,完成SOPC设计;5、支持SignalTapII 嵌入式逻辑分析仪。(2)USB到UART串行通信转换:1、通过USB与FPGA串行通信,实现PC与FPGA的串行通信,且无需RS232电平转换;2、通过USB与单片机的串行通信,实现PC与通用单片机的UART串行通信;3、通过USB对STC等系列单片机进行直接编程开发,无需电平转换。 ☆ ByteBlasterMV编程器一个(可对isp单片机编程)。 ☆ 5功能智能逻辑笔:可显示高电平、低电平、中电平、高阻态、脉冲信号。注意有“高阻态”测试功能。☆ 独立的标准时钟频率20个。20MHZ-0.5HZ。☆ 电源有自动保护的+5V,+12V、-12V、、+3.3V、2.5V+、1.2V。 ☆ 8个LED放光二级管,8个乒乓开关,扬声器。☆ DDS信号输出口及幅度、偏移调谐。

○ 基本软件:1)Quartus II 9.0/11.0;2)ModelSim;3)Synplify;4)IDE;5)8051单片机IP核;6)8088/8086 CPU IP核;7)8088/8086微机系统接口模块IP核:8253核、8237核、8259核、8255IP核和8250等IP核;8)Nios II和64MSRAM ★ 完成五大类实验项目 一、计算机组成原理与计算机体系结构类: ◇ 算术运算器、ROM、单双口RAM、FIFO、FPGA外部RAM/Flash存储器实验; ◇ 微控制器时序电路、乘法累加器设计、程序计数器与地址寄存器; ◇ 微控制器设计、总线控制器、锁相环应用、嵌入式逻辑分析仪应用等; ◇ 8位微程序控制的模型计算机的设计与实现。包括CPU设计,硬件指令设计,软硬件联合开发等; ◇ 基于FPGA的片上系统(SOC)的MCS-51单片机IP核实验与设计 ◇ 基于状态机的完整16位CPU设计。包括CPU设计,硬件指令设计,软硬件联合开发,SOC实现等; ◇ 基于流水线构架的16位RISC CPU设计及计算机体系结构相关实验; ◇ 基于FPGA的片上系统32位OPEN RISC软核嵌入式系统软硬件设计;◇ 计算机系统创新设计与实验。 二、硬件描述语言HDL与EDA/SOPC技术类实验和设计。 如移位相加硬件乘法器设计、用流水线技术设计高速数字相关器、线性反馈移位寄存器设计、VGA图像显示控制器设计、直接数字式频率合成器设计等实验。 三、基于单片FPGA的8086/8088 CPU核 8253/8254 IP核(定时器);8250 IP核(UART串行通信);8237 IP核(DMA控制器);8259 IP核(可编程中断控制器),锁相环核等经典IBM计算机系统设计。由于8086/8088核的全兼容性,传统微机原理及微机接口实验中的C和8086汇编程序都能直接由该核运行,完成基于EDA技术的微机原理及微机接口方面的部分实验。 四、全国大学生电子设计竞赛培训及开发。 能承担大学生电子设计竞赛中许多设计题目的培训任务,进一步强化计算机学生基于现代电子技术的硬件系统设计能力。 五、基于MATLAB和DSP Builder的全硬件高速DSP系统实验和设计 需要增配多通道超高速ADC/DAC适配板。 |