|

KX-EDA55A++)

收藏

EDA/SOPC实验与创新设计开发系统 型号:KX-EDA55A++由杭州电子科技大学潘松/黄继业编著的教材《EDA技术实用教程》自出版以来,发行量已超30万册,这在同类教材中绝无仅有。此书被先后评选为“十一五”和“十二五”国家级规划教材。科学出版社于建社55周年纪念日为此书作者潘松教授颁发了“优秀作者奖”,颁奖理由是“为表彰您为我社作出的突出贡献”;美国Altera公司为了表彰通过大发行量的广受欢迎的教材推广EDA/FPGA技术,在2011年的全国教师大会上特授予潘松教授“终身成就奖”。此教材在国内已有一百多所高校使用,其中还包括许多重点大学,如南大、哈工大、清华等。 清华大学许忠信教授对于此书参评国家级规划教材的评语是 “由潘松教授主编、科学出版社出版的<<EDA技术实用教程〉〉一书根据课堂教学和EDA实验的要求,以提高实际工程能力为目的,深入浅出地对EDA技术及相关知识做了系统和完整的介绍,是一本值得推荐的好教材。一本好教材来自于作者深厚的业务功底、长年的实践积累以及由此产生的先进的编撰理念,这些理念和独到视角均反映在作者撰写的前言中。比如通过典型实例讲解硬件描述语言,通过由浅入深、层层递进的实验项目培养学生的工程设计能力等等。在实验设计方面,既有与教材知识点紧密联系的基础性实验,以促进理论知识的掌握和基本技能的提高,又有开放的设计创新型实验,为培养学生创新能力留下了广阔空间。并且对于各类典型实验项目,均提供了较为详细的实验范例,方便了学生自学,提高了实验效率” 《EDA技术实用教程》有两个版本,VHDL版和VerilogHDL版。图中显示的是第4版的画面,但作者推荐选用第5版。第5版教材于今年5月出版。《EDA技术实用教程》的特色是: 1)注重实践、实用和创新能力的培养。 除在各章中安排了许多习题外,绝大部分章节都安排了许多针对性强的实验与设计项目,使学生对每一章的课堂教学内容和教学效果能及时通过实验得以消化和强化。并尽可能地从学习一开始就有机会将理论知识与实践及自主设计紧密联系起来。这些项目涉及的技术领域宽,知识涉猎密集、针对性强,而且自主创新意识的启示性好。与示例一样,所有的实验项目都通过了EDA工具的仿真测试并通过FPGA平台的硬件验证。每一个实验项目除给出详细的实验目的、原理和报告要求外,都含多个子任务,通常分为:第一层次实验任务是与该章某个阐述内容相关的验证性实验;第二层次实验任务是要求在上一实验基础上做一些改进和发挥;第三层次的实验通常是提出自主设计的要求和任务;在更高的实验任务层次则在仅给出一些提示的情况下提出自主创新性设计的要求。 2)高效的教学模式成就速成。 根据硬件描述语言的特点,摒弃流行的计算机语言的教学模式,而以电子线路设计为基点,采用了基于情景和工作过程的教学模式,从实例的介绍中引出HDL语句语法内容及深入浅出的教学流程,同时安排了大量对HDL学习有针对性的示例和实验项目,使读者能尽早进入数字系统工程设计经验的积累和能力提高阶段,并能通过这些面向实际的实践和实验活动,快速深化对HDL的理解,并掌握对应的设计技巧。 3)更加强调实践性。 此教材的结构特点决定了授课课时数可十分灵活,视具体的专业特点、课程定位及学习者的前期教育力度等因素而定,大致在20至50学时之间选择。为了有效倍增学生的实践和自主设计的时间,教材建议借鉴清华大学的一项教改措施,即其电子系本科生从一入学就人手获得一块FPGA实验开发板。这是因为EDA技术本身就是一个可把全部实验和设计带回家的课程。使他们能利用自己的计算机在课余时间完成自主设计项目,强化学习效果。 相比于前面4版,第五版的优势更为明显:1)语法的情景法描述更为直观,示例更为典型,结构更完整;2)对于工程设计十分重要的状态机应用一章有了更多的点睛之处,而在之后还增加了一章基于状态机的16位CPU详细设计的内容,将状态机的应用引向深入。特别是还加入了CPU创新设计竞赛项目和指导;3)鉴于Altera已将Quartus II 10.0及此后版本的软件中曾经一贯内置的门级波形仿真器移除了,并推荐使用接口于Quartus II的ModelSim仿真器,第五版针对Test Bench仿真,增加了ModelSim-Altera的使用方法;4)增加的另一章是介绍单片机与FPGA接口技术,及基于单片机IP核的FPGA片上系统开发的内容,这对电子设计竞赛培训很有用;5)删去了不太合适的实验项目和原来的SOPC内容(拟推相关教材)。

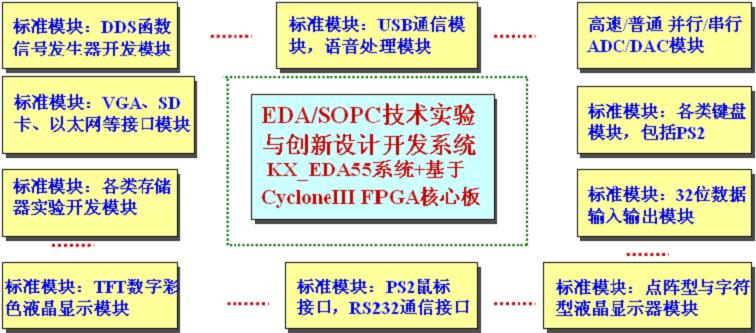

一、模块化EDA/SOPC实验与创新设计综合实验系统

KX_EDA结构示意图。由于以上介绍的4教材中大量的实验和设计项目涉及许多不同类型的,可自由增减的扩展模块,主系统平台上有许多标准接口。以其为核心,对于不同的实验设计项目,可接插上对应的接口模块。如VGA/PS2模块、TFT数字彩色液晶模块、USB模块、宽位数据输入输出模块、SD卡模块、点阵液晶模块、各类存储器模块、各类A/D与D/A模块及各类键盘模块等;这些模块可以是现成的,也可以根据主系统平台的标准接口和创新要求由教师或学生自行开发。 通常,诸如EDA技术、计算机组成与设计、微机原理与接口技术、单片机技术等传统实验平台多数是整体结构型的,虽也可完成多种类型实验,但由于整体结构不可变动,实验项目和类型是预先设定和固定的,很难有自主发挥的余地,对于学生的创新思想与创新设计如果与实验系统的结构不吻合,便无法在此平台上获得验证;同样,教师若有新的创新型实验项目,也无法及时融入实验系统供学生发挥。因此此类平台不具备可持续拓展的潜力,也没有随需要更新和升级的能力。特别是针对EDA/SOPC的创新实验,涉及的自主设计项目更多,结构变化更大,系统更复杂,完全不可能预知最后设计出的创新项目应该包含哪些功能结构和接口模块。显然,多模块自由组合结构给出了最好的解决方案。 不难理解,模块自由组合型创新设计综合实验系统,已成为高校目前十分流行的实践平台 以下向用户推荐几款从低到高实验系统,所配置的模块以序号来代替,或用户根据需要自行配置

型号:KX-EDA55A++完成以下实验:

KX-EDA系列系统所能实现的实验与创新设计项目类型包括: ▲ 现代数字电路与数字系统设计实验、基础EDA实验、针对VHDL/Verilog语言学习的实验与设计; ▲ EDA与SOPC创新设计实验与相关科研开发项目、全国大学生电子设计竞赛培训项目(注意,由于标准模块结构上的一般性,以及可以脱离主系统平台独立现成系统,因此模块可以直接用作电子竞赛的作品参加评审); ▲ 基于计算机原理与组织实验与设计,包括8位/16位CISC和RISC流水线型 CPU的设计、实现与测试; ▲ 基于32位Nios II嵌入式处理器和Qsys开发环境的SOPC实验与开发; ▲ 基于Open RISC 1200系列的32位RISC处理器嵌入式SOC系统实验与开发; ▲ 基于微机原理与接口技术的8088/8086 IP核的微机SOC系统,以及8253定时器IP核、8237 DMA IP核、8259中断控制IP核、8255可编程I/O IP核和8250 UART串行通信IP等核构建的单片FPGA SOC微机系统;此FPGA内部SRAM中含BIOS启动ROM、显示缓存、PS2缓存等;能启动MS-DOS操作系统和Windows操作系统,在VGA显示器上用PS2键盘和鼠标完成所有DOS和部分Windows命令及运行各种基于命令行的传统软件与视窗软件;单片机与FPGA接口实验与设计;基于8051单片机IP核的SOC片上系统设计系列实验等。 ○ 基本软件:1)Quartus II 9.0/13.0;2)ModelSim;3)Synplify;4)IDE;5)8051单片机IP核;6)8088/8086 CPU IP核;7)8088/8086微机系统接口模块IP核:8253核、8237核、8259核、8255IP核和8250等IP核;8)Nios II;

KX-EDA55A++配置如下: 一、基本平台 编号A ☆此平台最多可同时插12 块模块板。 ☆ KX_USB-Blaster2型双功能编程器:(1)USB-Blaster编程下载功能(支持AS、PS、JTAG模式):1、对FPGA/CPLD进行配置或编程;2、对配置器件EPCSx编程;3、访问和编辑FPGA内部RAM;4、调试Nios2,完成SOPC设计;5、支持SignalTapII 嵌入式逻辑分析仪。 (2)USB到UART串行通信转换:1、通过USB与FPGA串行通信,实现PC与FPGA的串行通信,且无需RS232电平转换;2、通过USB与单片机的串行通信,实现PC与通用单片机的UART串行通信;3、通过USB 对STC等系列单片机进行直接编程开发,无需电平转换。 ☆ ByteBlasterMV编程器一个(可对isp单片机编程)。 ☆ 5功能智能逻辑笔:可显示高电平、低电平、中电平、高阻态、脉冲信号。注意有“高阻态”测试功能。 ☆ 独立的标准时钟频率20个。20MHZ-0.5HZ。 ☆ 电源有自动保护的+5V,+12V、-12V、、+3.3V、2.5V+、1.2V。 ☆ 8个LED放光二级管,8个乒乓开关,扬声器。 ☆ DDS信号输出口及幅度、偏移调谐。

KX_DN系统部分实验

注:以下实验根据系统配置来对应完成

4.1 针对HDL设计的EDA基本实验与设计 实验4-1.计数器设计 实验4-2.多路选择器设计 实验4-3.8位全加器设计 实验4-4.原理图输入法设计频率计 实验4-5.十六进制7段数码显示译码器设计 实验4-6 数码扫描显示电路设计 实验4-7 半整数与奇数分频器设计 实验4-8 模可控计数器设计 实验4-9 VGA彩条信号显示控制电路设计 实验4-10 移位相加型8位硬件乘法器设计 实验4-11 移位寄存器设计 实验4-12 串行静态显示控制电路设计 4.2 针对LPM宏模块应用的EDA实验与设计 实验4-13.查表式硬件运算器设计 实验4-14. 正弦信号发生器设计 实验4-15. 八位数码显示频率计设计 实验4-16.简易逻辑分析仪设计 实验4-17. DDS正弦信号发生器设计 实验4-18. 移相信号发生器设计 实验4-19. 4X4阵列键盘键信号检测电路设计 实验4-20. VGA简单图像显示控制模块设计 实验4-21 SPWM脉宽调制控制系统设计 实验4-22 基于DES数据加密标准的加解密系统设计 实验4-23 线性反馈移位寄存器设计 实验4-24 步进电机细分控制电路设计 实验4-25 基于FT245BM的USB通信控制模块设计 实验4-26 直流电机综合测控系统设计 实验4-27 VGA动画图像显示控制电路设计 实验4-28 AM幅度调制信号发生器设计 4.3 针对状态机应用的EDA实验与设计 实验4-29 序列检测器设计 实验4-30 ADC采样控制电路设计 实验4-31 数据采集模块设计 实验4-32 五功能智能逻辑笔设计 实验4-33 比较器加DAC器件实现ADC转换功能电路设计 实验4-34 通用异步收发器UART设计 实验4-35 点阵型与字符型液晶显示器驱动控制电路设计 实验4-36 串行ADC/DAC控制电路设计 实验4-37 硬件消抖动电路设计 实验4-38 数字彩色液晶显示控制电路设计 实验4-39 状态机控制串/并转换8数码静态显示电路设计 实验4-40 基于FPGA的红外双向通信电路设计 4.4 EDA综合实验与设计 实验4-41 乐曲硬件演奏电路设计 实验4-42 正交幅度调制与解调系统实现 实验4-43 基于UART串口控制的模型电子琴设计 实验4-44 基于M9K RAM型LPM移位寄存器设计 实验4-45 单片全数字型DDS函数信号发生器综合设计 实验4-46 乒乓球游戏电路设计 实验4-47 PS2键盘控制模型电子琴电路设计 实验4-48 GPS应用的通信电路设计 实验4-49 在ModelSim上进行4位计数器仿真 实验4-50 在ModelSim上进行16位累加器设计仿真 第五章 SOPC实验与设计 实验5-1 基于SOPC的多功能数字钟设计 实验5-2 彩色液晶显示控制电路设计 实验5-3 基于Nios II的直流电机控制 实验5-4 自定制硬件乘法器 实验5-5 硬件乐曲演播系统设计 实验5-6 基于UART的I2C总线传输 实验5-7 基于Nios II的等精度频率计设计 第六章 单片机系统综合实验 6.1 单片机基本实验 实验6-1.存储器块清零程序设计 实验6-2 二进制到BCD转换程序设计 实验6-3 十六进制到ASCII码转换程序设计 实验6-4 存储块移动程序设计 实验6-5 多分支程序 实验6-6 数据排序程序设计. 实验6-7 P1口输入、输出实验 实验6-8 交通灯控制(软件延时法) 实验6-9 交通灯控制(定时器延时法) 实验6-10 计数器应用实验 实验6-11 外部中断实验 实验6-12 定时器实验1(P1口状态取反) 实验6-13 定时器输出PWM实验 实验6-14 外部中断实验 6.2 单片机扩展和接口实验与设计 实验6-15 单片机串口扩展 实验6-16 键盘与液晶显示控制 实验6-17 单片机串行通信和红外双向通信 实验6-18 单片机扩展X5045看门狗器件 实验6-19 单片机扩展DS1302时钟/日历器件 实验6-20 SPI串行DAC TLV5637与单片机的接口 实验6-21 串行精密ADC器件ADS1100与单片机的接口 实验6-22 串行高速ADC器件ADS7816与单片机的接口 实验6-23 高速微功耗串行ADC器件TLV2541与单片机的接口 实验6-24 双通道A/D转换芯片ADC0832与单片机的接口 实验6-25 高速同步10位串行A/D转换器与单片机的接口 第七章 单片机扩展FPGA综合实验与设计 实验7-1 单片机串行扩展FPGA系统设计 实验7-2 单片机数据交换FPGA扩展电路设计 实验7-3 扩展外部数据存储器的单片机与FPGA扩展系统设计 实验7-4 四通道PWM信号发生器及其单片机控制系统设计 实验7-5 移相信号发生器的FPGA与单片机扩展系统设计 实验7-6 里萨如图波形发生器的单片机与FPGA扩展系统设计 实验7-7 数字电压表FPGA单片机的系统设计 实验7-8 数字频率计与单片机串行通信接口功能设计 实验7-9 直流电机测控单片机与FPGA扩展系统设计 实验7-10 等精度频率/脉宽/占空比/相位多功能测试仪设计 第八章 基于单片机8051/8088微机原理IP核的FPGA片上系统SOC设计 实验8-1.单片机串口扩展FPGA片上系统SOC设计 实验8-2.扩展外部数据存储器的FPGA单片系统设计 实验8-3.四通道PWM信号发生器及单片系统设计 实验8-4.移相信号发生器的FPGA片上系统SOC设计 实验8-5.里萨如图波形发生器的FPGA片上系统设计 实验8-6.数字电压表FPGA单片系统SOC设计 实验8-7.数字频率计与单片机串行通信接口功能设计 实验8-8.直流电机测控FPGA单片系统设计 实验8-9.等精度频率计FPGA单片系统设计 实验8-10.基于FPGA的红外双向通信单片系统设计 实验8-11. 频率和占空比可数控方波信号发生器设计示例 实验8-12. 8052 IP核等精度频率计/GPS应用联合设计 实验8-13. 8051核控制DS18B20数字温度模块 实验8-14. 8051核驱动LCD128X64 实验8-15. 基本8088和8253核应用 实验8-16. 基本8088系统的GPS应用模块 实验8-17. 8088系统的DMA核应用 实验8-18. 8088系统UART核应用 实验8-19. 8086经典微机片上系统构建

|